| |||||||

|

|

|

||||||

|

|

|

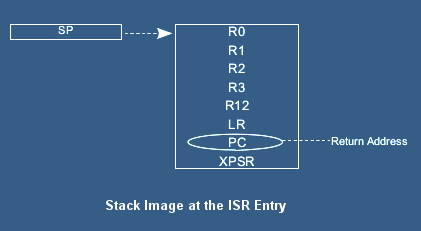

Testing protection of critical sections and behavior when an interrupt appears In order to provide in-depth testing the DioneOS System in the time domain, its protection in critical sections and to confirm ARM Cortex-M3 behavior controlled interrupt forcing method was applied (figure below).  High resolution hardware timer was used in the tests. The timer was programmed to trigger interrupt after set delay. In this way it is possible to force the interrupt in specified program location. This type of test was executed mutiple time using consecutive value of the delay. An Address where interrupt appeared (see below stack image) together with other parameters were stored for each iteration. Such a test provided scanning critical location in the code and checking all possible cases (i.e. preemption because of different priorities, interrupt states including pending and active-pending one). Determination of location where the interrupt appeared After triggering the interrupt ARM Cortex-M3 stores on teh stack basic registers (i.e. XPSR, PC, R12, LR, R0-R3). They are stacked by hardware accoring to below image.

Using stack contents in ISR it is possible to determine return address and indirectly where the interrupt appeared. Additional test consists in LR register contents check that provides information if the interrupt is nested. Advanced behavior of ARM Cortex-M3

During the tests used methods provided observation of advanced ARM Cortex-M3 bahavior:

*)-. If it needs to be avoided the barrier should be used. |

|

||||

|

|

|||||||