| |||||||

|

|

|

||||||

|

|

|

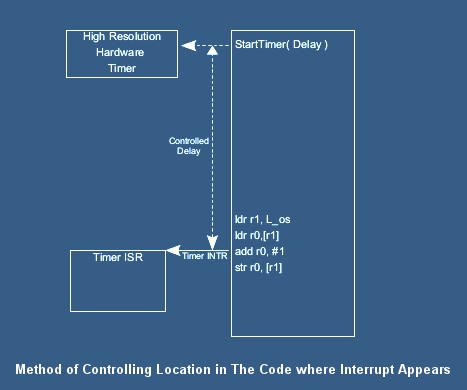

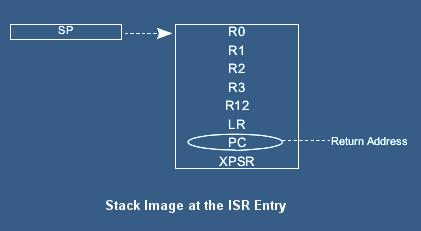

Testowanie zabezpieczenia sekcji krytycznych i zachowania podczas pojawienia się przerwania W celu dokładnego przetestowania działania systemu DioneOS pod względem poprawności zabezpieczenia sekcji krytycznych oraz potwierdzenia zachowania procesora ARM Cortex-M3 zastosowano metodę kontrolowanego wywoływania przerwania (rys. poniżej).  Wykorzystano do tego celu timer sprzętowy o wysokiej rozdzielczości, który wyzwalał przerwanie po upłynięciu ustawianego opóźnienia. W ten sposób możliwe było spowodowanie przerwania w określonym miejscu programu. Tego typu test wykonano wielkokrotnie, dla kolejnych wartości opóźnienia rejestrując miejsce wystąpienia przerwania (patrz ponizej obraz stosu) oraz inne parametry. W ten sposób możliwe było sprawdzenie działania dla wszystkich możliwych przypadków (m.in. wywłaszczanie przerwań z powodu różnych priorytetów, stanu przerwań, w tym przerwań oczekujących czy nawet aktywnych-oczekujacych). Określanie miejsca wystąpienia przerwania Po wstąpieniu przerwania procesor ARM Cortex-M3 odkłada na stosie podstawowe rejestry (t.j. XPSR, PC, R12, LR, R0-R3). Są one odkładane sprzętowo wg poniższego obrazu.

Analizując zawartość tej części stosu po wejściu w ISR można wywnioskować w jakim miejscu programu zostało wywołane przerwanie. Dodatkowo można sprawdzać zawartość rejestru LR, który zawiera informację o tym czy przerwanie przerwało obsługę innego (zagnieżdżone przerwania). Zaawansowane cechy ARM Cortex-M3

Za pomocą stosowanych metod możliwa była obserwacja zaawansowanych cech procesora ARM Cortex-M3 takich jak:

*)-. Jeśli jest to niekorzystne należy zastosować barierę. |

|

||||

|

|

|||||||