Rejestry QPU

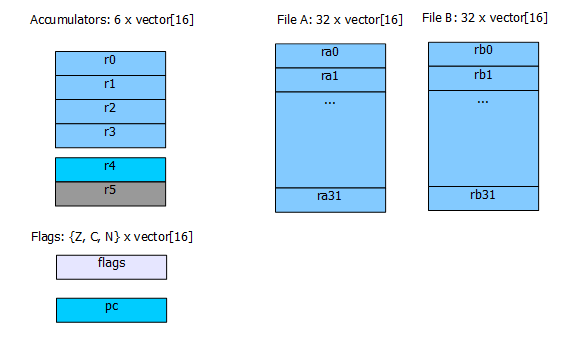

Procesor QPU zawiera kilka akumulatorów i dwa duże zestawy rejestrów. Każdy z rejestrów (wliczając akumulatory) może przechowywać wektor elementów,

więc jest dostosowany do wykonywania operacji SIMD.

Są 4 akumulatory ogólnego przeznaczenia, które można swobodnie używać oraz 2 o specjalnej funkcji.

W kazdym zestawie rejestrów jest ich 32. Zestawy te, jak i zawarte w nich rejestry są oznaczone literami a i b.

Wszystkie rejestry z tych dwóch zestawów tworzą łącznie lokalną pamięć, właściwą dla każdego procesora QPU z osobna.

Rys. 4. Rejestry QPU.

Akumulatory i rejestry z zestawów różnia się:

- długością ścieżki w potoku QPU, stąd wynik w akumulatorze jest dostępny już w następnej instrukcji,

- elastycznością użycia w jednej instrukcji - są pewne ograniczenia w użyciu rejestrów z zestawów,

- rotacja wektora może być tylko wykonywania na akumulatorach,

- liczba akumulatorów jest niewielka.

Ze względu na swoje własności rejestry z zestawów dobrze nadają się na przechowywanie zmiennych oraz przeznaczonych do późniejszego użycia konfiguracji.

Jednocześnie akumulatory powinny być często używane w obliczeniach, i gdy uzyskana będzie końcowa wartość należy ją zapisać w rejestrze z zestawu.

Można powiedzieć, że akumulatory służą do przechowywania wyników pośrednich, podczas gdy rejestry z zestawów mają jakieś przypisane znaczenie (przez programistę)

w trakcie działania programu (tak jak zmienne globalne w językach wysokiego poziomu).

Powiązane moduły sprzętowe (Closely Coupled Hardware)

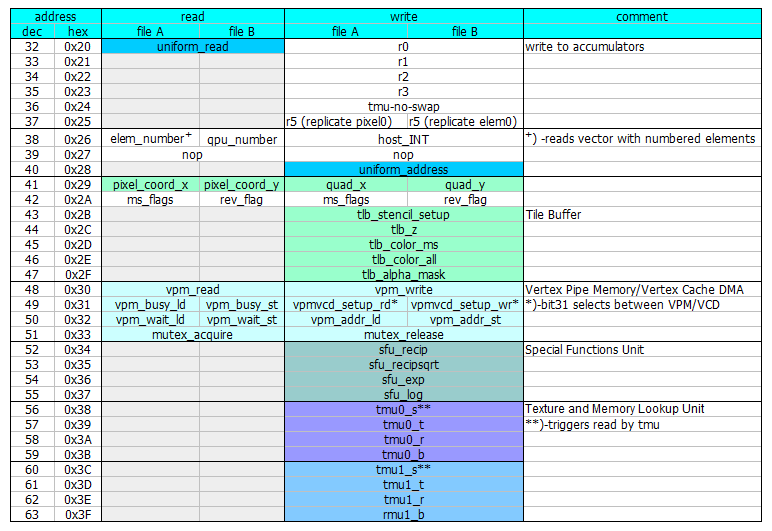

Procesor QPU może kontrolować hardware który jest z nim powiązany (np.: Vertex Pipe Memory, DMA, Texture and Memory Lookup Unit, Special Functions Unit, etc.).

Te moduły sprzętowe są dostępne poprzez przestrzeń adresową rejestrów z zestawów - adresy powyżej 31 są uzywane do tego celu.

Z punktu widzenia programisty moduły zachowują się podobnie jak zwykłe rejestry, więc normalne instrukcje mogą wykonywac na nich operacje.

Rys. 5. Przestrzeń adresowa używana do dostępu do powiązanych modułów sprzętowych.

Instrukcje QPU

Procesor QPU posiada jednolity 64-bitowy format instrukcji (każda instrukcja ma tą samą dlugość). W prawdzie liczba typów instrukcji jest niewielka

ale dzięki dużemu rozmiarowi pojedynczej instrukcji są one elastyczne. Są nastepujące typy instrukcji:

- instrukcje ALU,

- instrukcje ładowania

- instrukcje skoków

- instrukcje synchronizacji (semaphory)

Instrukcje kontrolują dwudrożne ALU, które może wykonywać dwie operacje jednocześnie. Jedna ścieżka ALU jest odpowiedzialna za operacje dodawania,

a druga wykonuje mnożenia i rotację wektora.

Procesor posiada potok (instruction pipeline), który nie jest opróżniany gdy wykonuje skok, stąd w przykładowych programach można znaleźć dziwne sekwencje

instrukcji. Po instrukcji skoku umieszczane są 3 dodatkowe, nieoczekiwane linie:

1 :entry

2 brr -, r:loop1

3 nop ; ldtmu0

4 mov r0, r4 ; ldtmu0

5 mov r1,r4

Oznacza to, że te trzy linie (3,4,5) bedą wykonane po skoku ale przed pierwaszą instrukcją, która jest umieszczona pod adresem docelowym skoku.

Dzieje się tak, bo te trzy instrukcje pozostają już w potoku, gdy skok jest wykonywany.

Szczegóły instrukcji procesora QPU można znaleźć w dokumentacji producenta układu VideoCore IV 3D (zobacz (1) w sekcji linki poniżej).

Warto przeczytać też Addendum (linki (2) poniżej) gdzie Marcel Muller, autor makroasemblera do videocore'a wyjaśnia pewne specyficzne cechy

instrukcji, niezgodności i nieudokumentowane własności.

Główne ograniczenia instrukcji

W związku ze specyfiką architektury procesora QPU można zaobserwować poniższe ograniczenia:

- wynik zapisany do rejestru z zestawu nie jest dostępny dla następnej instrukcji,

- jedna instrukcja nie może używać więcej niż jednego rejestru z tego samego zestawu

- mała stała nie może być używana razem z reejstrem z zestawu B

- rotacja wektora musi być wykonywana na akumulatorze

- akumulator na którym jest wykonywana rotacja nie może być zapisywany w poprzedniej instrukcji

- formaty pakowane są obslugiwane tylko przez rejestry z zestawu A, oraz akumulator r4

- procesor nie posiada stosu sprzętowego, do przechowywania adresu powrotu należy użyć wybranego rejestru z zestawu rejestrów A -

odpowiednik link register w architekturze ARM

- jeśli wyniki obu ścieżek ALU (add i mul) są zapisywane do zestawu rejestrów, muszą to być rejestry z różnych zestawów